Chipmakers face big challenges at 10nm and beyond

Fifty years after Gordon Moore first described the trend that has driven technology, Intel says scaling is same as it ever was. But other chipmakers, who are struggling to realize the same benefits from good old-fashioned scaling, are increasingly looking for less-expensive alternatives.

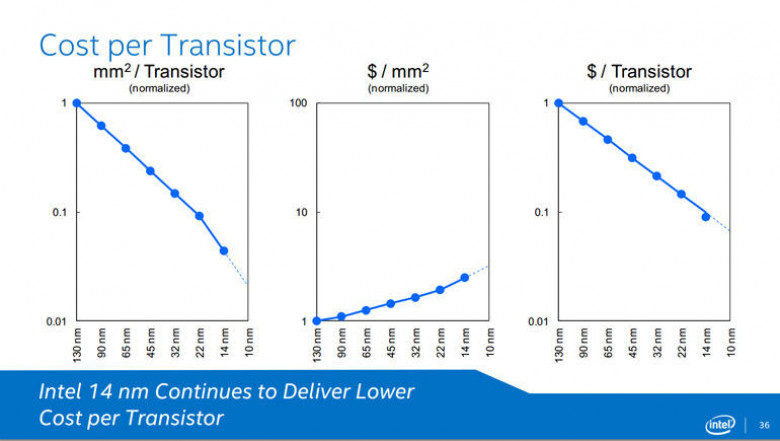

At a panel sessions on the future of Moore's Law at ISSCC, one of the chip industry's main events taking place in San Francisco, Intel's Mark Bohr said that even though "we've all been struggling with increasing rates of wafer costs," the company continued to increase transistor density and reduce cost per transistor at the same rate--perhaps even a little faster at 14nm. He added that the future 10nm and 7nm nodes will also provide both scaling and "ever lower cost per transistor."

This will require new innovation, but Bohr said this has always been the case--most recently with the introduction of high-k materials and metal gates at 45nm and 3D transistors or FinFETs at 22nm. This will take us to 10nm and most likely to 7nm, but beyond that the industry may need more radical solutions including the use of new materials in the channel, the conductive band between the source and drain in a transistor, and new structures such as gate-all-around nanowires or tunnel FETs. The way forward has always seemed "inordinately difficult," Bohr said, but the industry finds a way to continue scaling.